### A 4.2-9.2GHz Cryogenic Transformer Feedback Low Noise Amplifier with 4.5K Noise Temperature and Noise-Power Matching in 22nm CMOS FDSOI

Boce Lin<sup>1,5</sup>, Hamdi Mani<sup>2</sup>, Phil Marsh<sup>3</sup>, Richard Al Hadi<sup>4</sup>, Hua Wang<sup>1,5</sup>

<sup>1</sup>School of ECE, Georgia Tech, USA

<sup>2</sup>CryoElec LLC, USA

<sup>3</sup>Carbonics Inc, USA

<sup>4</sup>Alcatera Inc, USA

<sup>5</sup>ETH Zurich, Switzerland

- Introduction

- Circuit Implementation

- Simultaneous Noise and Power Matching

- Transistor Optimization

- Transformer Feedback

- Cryogenic Applications

- Measurement Results

- Summary

- Introduction

- Circuit Implementation

- Simultaneous Noise and Power Matching

- Transistor Optimization

- Transformer Feedback

- Cryogenic Applications

- Measurement Results

MTT-S

• Summary

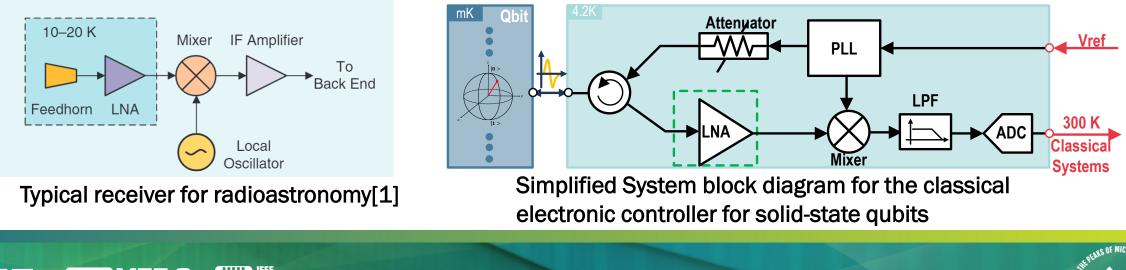

- Cryogenic electronic circuits applications

- > Deep space applications, Planetary applications, Radioastronomy, ...

- Quantum computation applications

- $\rightarrow$  Classical electronic controller as intermediate interface between mK environment and room temperature environment

- Cryogenic CMOS controller

- $\rightarrow$  Existing large scale integration capability

- $\rightarrow$  Compatible with semiconductor Qubits

- Cryogenic CMOS low noise amplifier (LNA)

- Required in most of the read-out systems to amplify the extremely weak read-out signal

- Frequency multiplex requires a broadband operation

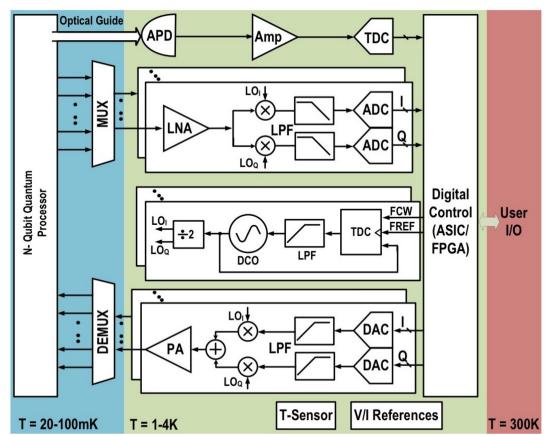

Example of multi-channel classical interface to a

quantum processor. [2]

- Cryogenic LNA specifications for gate dispersive qubits read-out [3]

- Operation Frequency: 4GHz 8GHz

- Noise figure (NF): < 0.8 dB

- Gain: > 40dB

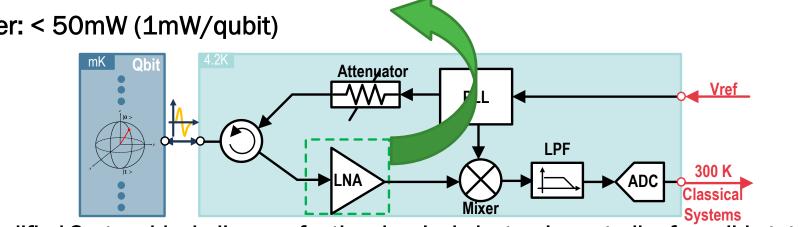

- Power: < 50mW (1mW/qubit)

Simplified System block diagram for the classical electronic controller for solid-state Qubits

6

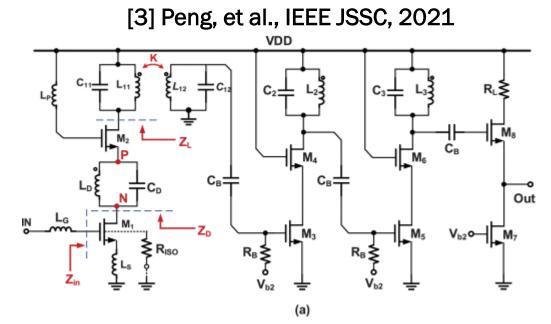

- Frequency: 4.6-8.2 GHz

- NF: 0.23-0.65dB

- Inductive degenerated Common source

SOLID-STATE

- Frequency: 0.1-0.5 GHz

- NF: 0.1-0.8dB

- Noise Canceling

- No broadband simultaneous

- power-noise matching

- Introduction

- Circuit Implementation

- Simultaneous Noise and Power Matching

SÕLID-STATE

- Transistor Optimization

- Transformer Feedback

- Cryogenic Applications

- Measurement Results

- Summary

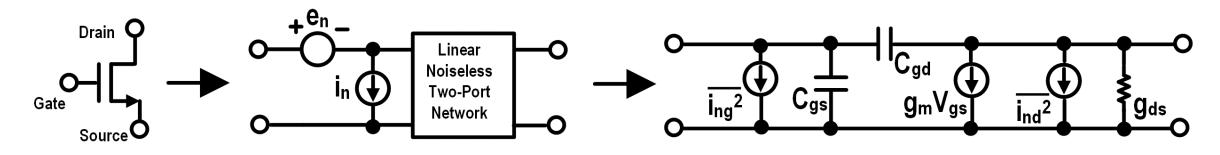

# Simultaneous Power and Noise Matching

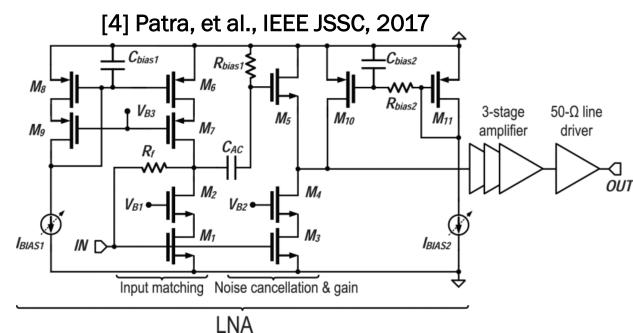

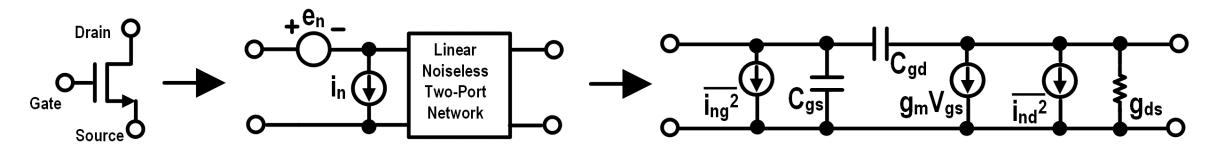

- Simple equivalent noise circuit for MOSFET device has been studied previously [5]

- Gate Induced Noise Current Source:  $\overline{i_{ng}^2} = \frac{4kT\Delta f\delta\omega^2 C_{gs}^2}{5g_{d0}}$  ( $\delta$ : The Excess Gate Noise Coefficient

- Drain Noise Current Source:  $\overline{i_{nd}^2} = 4 \text{kT} \Delta f \gamma g_{d0}$

- Noise Source Correlation Coefficient:  $c = \frac{\overline{i_{nd}^* i_{ng}}}{\sqrt{i_{nd}^2 i_{ng}^2}}$ •

- *y*: The Excess Drain Noise Coefficient

- $g_{d0} = \frac{g_m}{\alpha}$  is the output conductance when Vds = OV

- As discussed in [6], this two-port network achieves the minimum noise figure when:

- $\begin{cases} G_{opt} = \omega C_{gs} \psi \\ B_{opt} = -\omega C_{gs} \xi \end{cases}, \qquad Where \quad \begin{aligned} \psi = \alpha \sqrt{(1 |c|^2)\delta}/5\gamma \\ \xi = 1 \alpha |c|\sqrt{\delta}/5\gamma \end{cases}$

- Achievable minimum Noise figure is independent of the value of source inductor

• [6] shows that simultaneous power and noise matching is achieved when:

$\psi^2 + \xi^2 = \xi$

11

- 22nm CMOS FDSOI has low intrinsic  $C_{gs}$  at frequency band of interests

$\rightarrow$ External Cgs is added to provide an additional degree of freedom

- The noise parameters are dependent of frequency

- We follow the following design procedures:

$$\begin{array}{c}

G_{opt} = \omega(C_{gs,ext} + C_{gs,int})\psi \\

B_{opt} = -\omega(C_{gs,ext} + C_{gs,int})\xi \\

\downarrow \text{Obtain} \\

\psi = \alpha\sqrt{(1 - |c|^2)\delta/5\gamma} \\

\xi = 1 - \alpha|c|\sqrt{\delta/5\gamma}

\end{array}$$

$$\begin{array}{c}

C_{gs,ext} \text{ tuning} \\

\psi^2 + \xi^2 = \xi \\

\downarrow \text{Obtain} \\

\psi^2 + \xi^2 = \xi \\

\downarrow \text{Obtain} \\

\downarrow \text{Obtain} \\

\xi = 1 - \alpha|c|\sqrt{\delta/5\gamma}

\end{array}$$

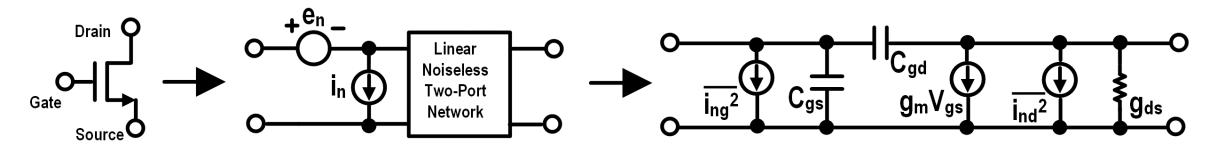

## Core Transistor Optimization

- First common source transistor width is fixed at 220  $\mu m/20 nm$

- Break down the large transistor into several smaller parallel transistors

- $\rightarrow$  Improve minimum noise figure

- $\rightarrow$  Improve associated gain

- In this design:

- 6 unit-transistors are combined

- Unit transistor size: 35 µm/20nm

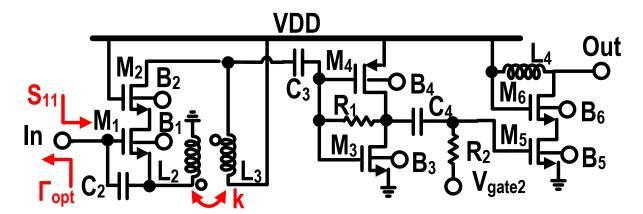

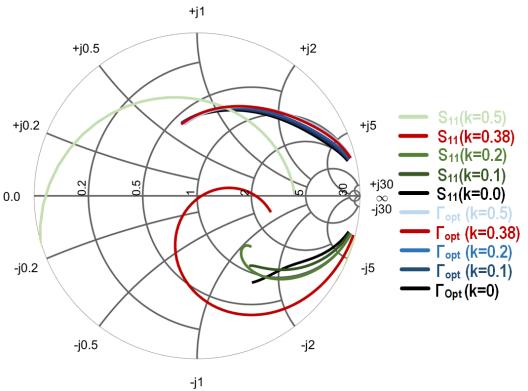

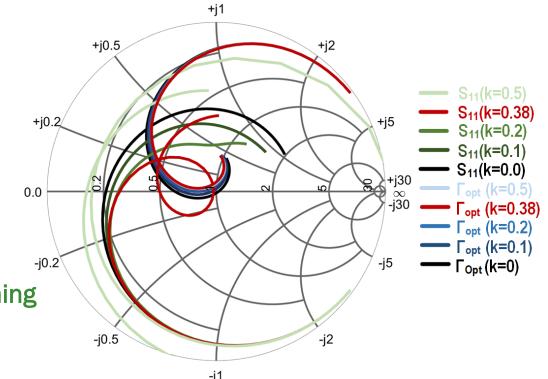

- Coupling factor (k) increase → Improve Power Matching

- Strongly coupled drain and source → Unstable Amplifier

- Optimum noise refection coefficient ( $\Gamma_{opt}$ ) remains nearly unchanged

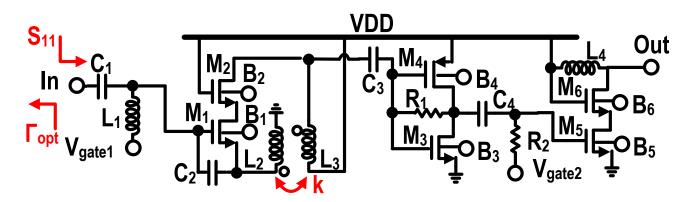

- Add input matching network

- $\rightarrow$  Achieve broadband simultaneous noise-power matching

- $\rightarrow$  Add loss which degrades total noise figure

- Broadband power and noise matching can be achieved by properly chosen k and input matching network

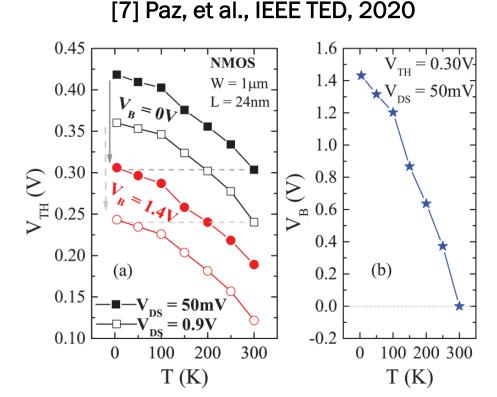

- Based on [7], the following changes are considered to design the active devices at cryogenic temperature:

- Increase threshold voltage ( $V_{th}$ )

- $\rightarrow$  Apply backgate bias can shift the V<sub>th,cryo</sub> = V<sub>th,RT</sub>

- Increase the effective mobility due to the suppression of phonon scattering contribution

- $\rightarrow$  Affects power matching conditions

- $\rightarrow$  Simulate the response with increased gm

- Based on [8], the following changes are considered to design the passive EM components at cryogenic temperature:

- Metal conductivity increases five-folds

- → Metal Impurity

- The substrate resistivity increases 1000x

→ Carrier Freeze-Out Effect

- Introduction

- Circuit Implementation

- Simultaneous Noise and Power Matching

- Transistor Optimization

- Transformer Feedback

- Cryogenic Applications

- Measurement Results

MTT-S

SSCS

IEEE SOLID-STATE 18

Summary

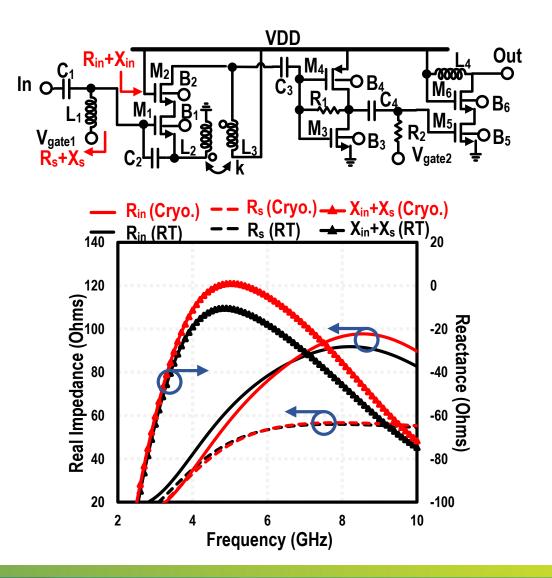

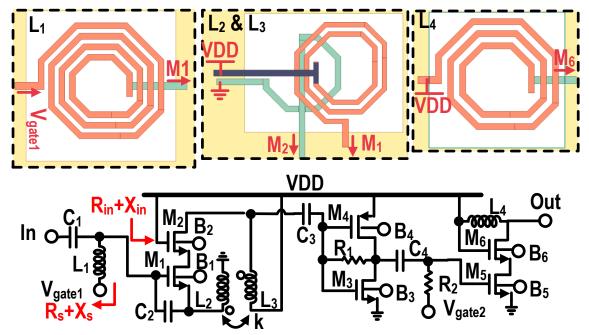

• The implemented circuit schematic and components values

SOLID-STATE

| Lı             | $L_2$            | L <sub>3</sub> | $L_4$      | Cı                    |  |

|----------------|------------------|----------------|------------|-----------------------|--|

| 1.05nH         | 300pH            | 1.15nH         | 1nH        | 1pF                   |  |

| C <sub>2</sub> | C3               | C4             | <b>R</b> 1 | <b>R</b> <sub>2</sub> |  |

| 200fF          | 1pF              | 1pF            | 350Ω       | 1ΚΩ                   |  |

| k              | $\mathbf{M}_{1}$ | M2-3, M5-6     | $M_4$      | Vdd                   |  |

| 0.38           | 35µm/20nm<br>x6  | 60µm/20nm      | 80µm/20nm  | 0.8V                  |  |

RM<u>01B-1</u>

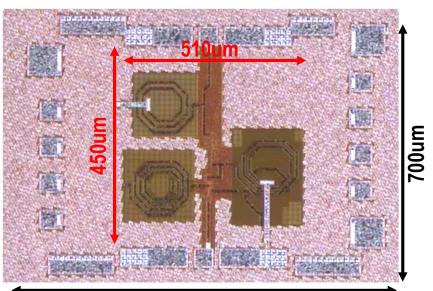

- The design is implemented in GlobalFoundries 22nm FDSOI CMOS technology

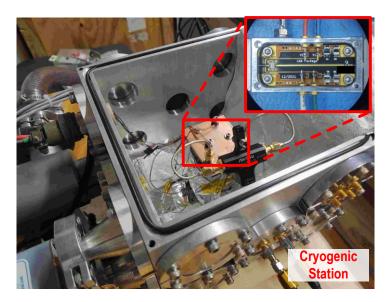

- The chip is packaged in a custom designed chassis within the cryogenic station

**Cryogenic Measurement Setup**

**ÖLID-STATE**

880um Chip Microphotograph

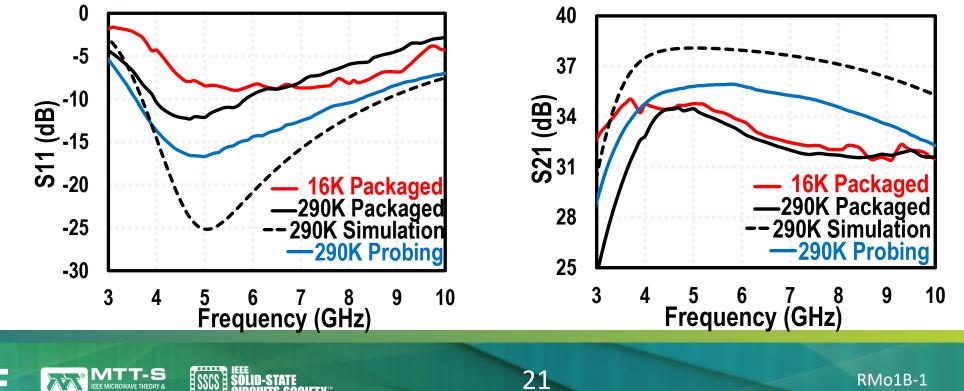

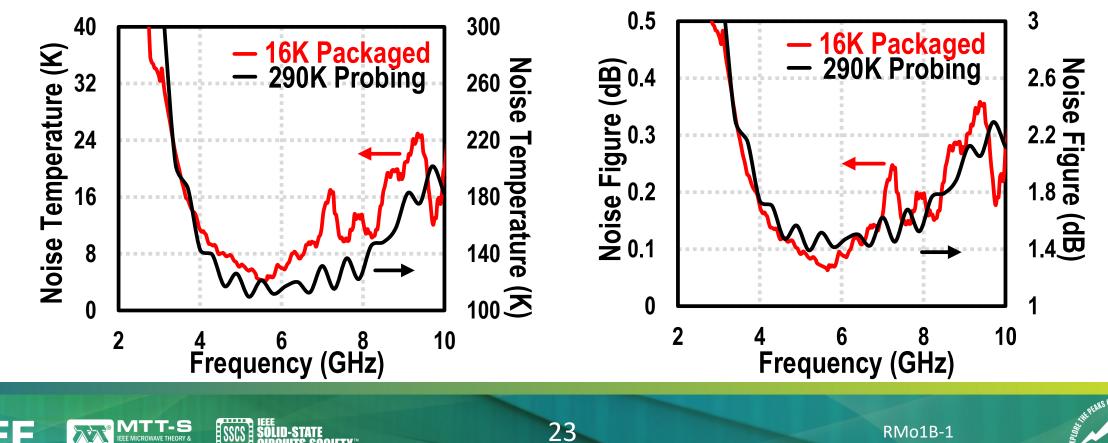

- The design is measured at 16K and 300K

- At 300K, S<sub>11</sub><-10dB from 3.6GHz to 8.2GHz with 34~35.9dB gain

- At 16K, S<sub>11</sub><-5.6dB from 4.2GHz to 9.2GHz with 31.4~34.7dB gain

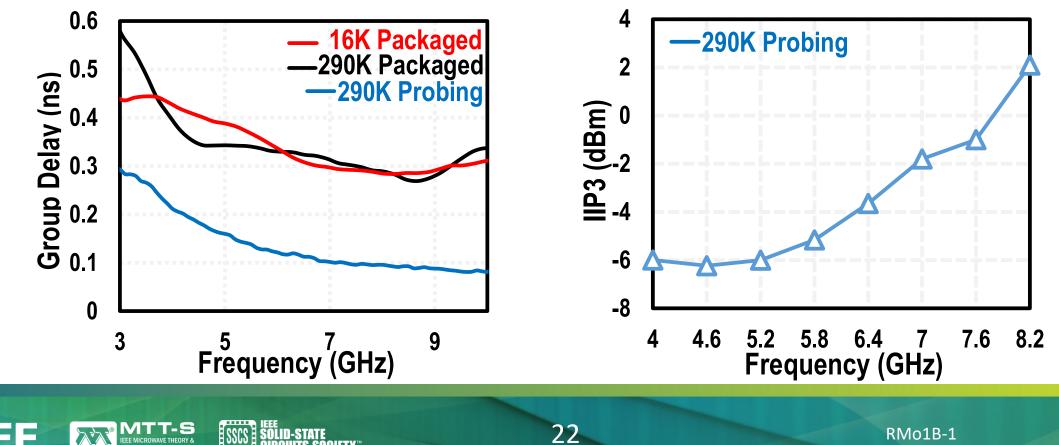

- At 300K, the total group delay is less than 0.3ns and  $IIP_3 > -6dBm$

- At 16K, the total group delay is less than 0.42ns

- At 300K, the measured noise temperature is 115.1 ~153K (1.41dB~1.79dB)

- At 16K, the measured noise temperature is 4.5~21.5K (0.065dB~0.3dB)

**DENVER2022**

- Introduction

- Circuit Implementation

- Simultaneous Noise and Power Matching

- Transistor Optimization

- Transformer Feedback

- Cryogenic Applications

- Measurement Results

MTT-S

SSCS

IEEE SOLID-STATE

• Summary

## Comparison Table

|                         | This                                        | This Work JSSC '21 [4] |                                     | TMTT '18 [1]  |                   | TCS '19[2]     |                 | JSSC '18[9]  |                  |               |

|-------------------------|---------------------------------------------|------------------------|-------------------------------------|---------------|-------------------|----------------|-----------------|--------------|------------------|---------------|

| Topology                | SNPM + XFMR FB +<br>Current Reuse + Cascode |                        | Cascode +R-C loading<br>+ XFMR load |               | 3 Stage Cascade   |                | Cascode CS      |              | Noise Cancelling |               |

| Vdd (V)                 | 0.8                                         |                        | 1.4                                 |               | 2                 |                | 1.8             |              | 1.4              |               |

| Frequency (GHz)         | 3.6~8.2                                     | 4.2~9.2                | 4.1~7.9                             | 4.6~8.2       | 0.3               | ~14            | 2.0~2.12        |              | 0.1~0.5          |               |

| Meas. Temp. (K)         | 300                                         | 16 <sup>†</sup>        | 300                                 | 4.2           | 300               | 4              | 300             | 77           | N/A              | N/A           |

| Power (mW)              | 28                                          | 21                     | 51.1                                | 39            | 100               | 12             | N/A             | 15           | 300              | 4.2           |

| Gain(dB)                | 34~<br>35.9                                 | 31.4~<br>34.7          | 35.5~<br>36.5                       | 39.2~<br>44.8 | 39.8~<br>41.6     | 40.2 ~<br>43   | 15              | 18           | 35~40            | 50~58         |

| Noise Temp. (K)         | 115.1~<br>153                               | 4.5~21.5               | 54.7~<br>101.2                      | 16.3~<br>48.4 | 60.7~<br>125      | 2.2~13         | 121.5~<br>159.2 | 35.4         | 35.4<br>~ 96.7   | 6.8~<br>62.7  |

| NF $(dB)^{}$            | 1.41~1.79                                   | 0.065~0.3              | 0.73~1.26                           | 0.23~0.65     | 0.80~<br>1.51     | 0.03 ~<br>0.18 | 1.52 ~<br>1.9   | 0.48         | 0.8 ~<br>1.25    | 0.1 ~<br>0.85 |

| \$11 (dB)               | -16.7~<br>-10.2                             | -8.9~<br>-5.6          | -22~<br>-12                         | -26~<br>-5.8  | -22~<br>-1        | -22 ~ -<br>6   | -10 ~<br>-6     | -40 ~<br>-15 | -9~<br>-5        | -7 ~<br>-3    |

| Area (mm <sup>2</sup> ) | 0.23*                                       |                        | 0.72                                |               | 1.5               |                | N/A             |              | 0.249            |               |

| Technology              | 22nm CMOS FDSOI                             |                        | 40nm CMOS                           |               | 100nm InP<br>HEMT |                | 0.18µm CMOS     |              | 0.16µm CMOS      |               |

†: Temperature is limited by testing equipment. \*: Core Area. ^: NF is referring to 300K

MTT-S IEEE MICROWAVE THEORY &

- The implemented cryogenic CMOS LNA provide wideband 4.2GHz to 9.2GHz operation bandwidth for quantum applications.

- The implemented LNA provides broadband simultaneous noise and power matching using transformer feedback at cryogenic temperature.

- It paves the way for future quantum applications with large scale qubits integration

- Amy STTR program for sponsoring this design

- Dr. Joe Qiu for supporting this design

- GlobalFoundries for chip fabrication

- Members at Georgia Tech GMES lab for technical discussion

[1] C.-C. Chiong, et al., "Low-Noise Amplifier for Next-Generation Radio Astronomy Telescopes: Review of the State-of-the-Art Cryogenic LNAs in the Most Challenging Applications," IEEE Microw Mag, vol. 23, no. 1, pp. 31–47, 2022, doi: 10.1109/mmm.2021.3117318.

[2] E. Charbon et al., "15.5 Cryo-CMOS Circuits and Systems for Scalable Quantum Computing," 2017 IEEE Int Solid-state Circuits Conf Isscc, pp. 264–266, 2017, doi: 10.1109/isscc.2017.7870362.

[3] Y. Peng, et al., "A Cryogenic Broadband Sub-1-dB NF CMOS Low Noise Amplifier for Quantum Applications," leee J Solid-st Circ, vol. 56, no. 7, pp. 2040–2053, 2021, doi: 10.1109/jssc.2021.3073068.

[4] B. Patra et al., "Cryo-CMOS Circuits and Systems for Quantum Computing Applications," in IEEE Journal of Solid-State Circuits, vol. 53, no. 1, pp. 309-321, Jan. 2018, doi: 10.1109/JSSC.2017.2737549.

[5] M. W. Pospieszalski, "Interpreting Transistor Noise," leee Microw Mag, vol. 11, no. 6, pp. 61–69, 2010, doi: 10.1109/mmm.2010.937733.

[6] E. Zailer, et al., "Wideband LNA Noise Matching," leee Solid-state Circuits Lett, vol. 3, pp. 62–65, 2020, doi: 10.1109/lssc.2020.2986645.

[7] B. Cardoso Paz et al., "Performance and Low-Frequency Noise of 22-nm FDSOI Down to 4.2 K for Cryogenic Applications," in IEEE Transactions on Electron Devices,

vol. 67, no. 11, pp. 4563-4567, Nov. 2020, doi: 10.1109/TED.2020.3021999.

[8] B. Patra, et al., "Characterization and Analysis of On-Chip Microwave Passive Components at Cryogenic Temperatures," in IEEE Journal of the Electron Devices Society, vol. 8, pp. 448-456, 2020, doi: 10.1109/JEDS.2020.2986722.